4 tommer SiC Wafers 6H semi-isolerende SiC substrater prime, forskning og dummy kvalitet

Produkt specifikation

| karakter | Zero MPD Production Grade (Z Grade) | Standard produktionskvalitet (P-klasse) | Dummy Grade (D Grade) | ||||||||

| Diameter | 99,5 mm~100,0 mm | ||||||||||

| 4H-SI | 500 μm±20 μm | 500 μm±25 μm | |||||||||

| Wafer orientering |

Off-akse: 4,0° mod< 1120 > ±0,5° for 4H-N, On-akse: <0001>±0,5° for 4H-SI | ||||||||||

| 4H-SI | ≤1 cm-2 | ≤5 cm-2 | ≤15 cm-2 | ||||||||

| 4H-SI | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |||||||||

| Primær flad orientering | {10-10} ±5,0° | ||||||||||

| Primær flad længde | 32,5 mm±2,0 mm | ||||||||||

| Sekundær flad længde | 18,0 mm±2,0 mm | ||||||||||

| Sekundær flad orientering | Silicium med forsiden opad: 90° CW.fra Prime flat ±5,0° | ||||||||||

| Kantudelukkelse | 3 mm | ||||||||||

| LTV/TTV/Bow/Warp | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| Ruhed | C ansigt | Polere | Ra≤1 nm | ||||||||

| Si ansigt | CMP | Ra≤0,2 nm | Ra≤0,5 nm | ||||||||

| Kantrevner af lys med høj intensitet | Ingen | Kumulativ længde ≤ 10 mm, enkelt længde≤2 mm | |||||||||

| Hex plader af høj intensitet lys | Akkumuleret areal ≤0,05 % | Akkumuleret areal ≤0,1 % | |||||||||

| Polytype områder med høj intensitet lys | Ingen | Akkumuleret areal≤3 % | |||||||||

| Visuelle kulstofindeslutninger | Akkumuleret areal ≤0,05 % | Akkumuleret areal ≤3 % | |||||||||

| Siliciumoverfladeridser af lys med høj intensitet | Ingen | Kumulativ længde≤1*waferdiameter | |||||||||

| Edge Chips High By Intensity Light | Ingen tilladt ≥0,2 mm bredde og dybde | 5 tilladte, ≤1 mm hver | |||||||||

| Siliciumoverfladeforurening med høj intensitet | Ingen | ||||||||||

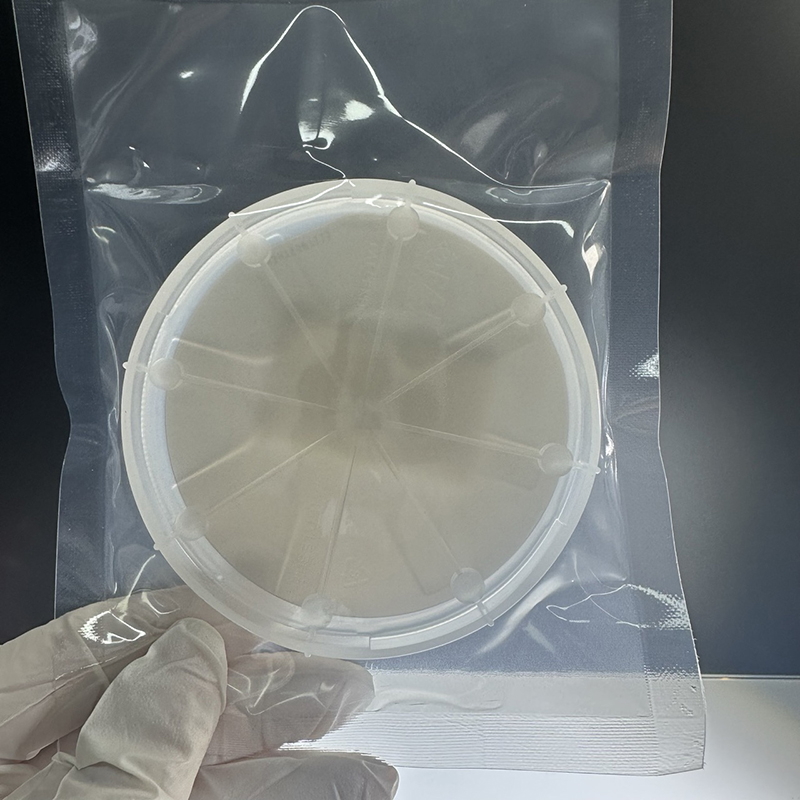

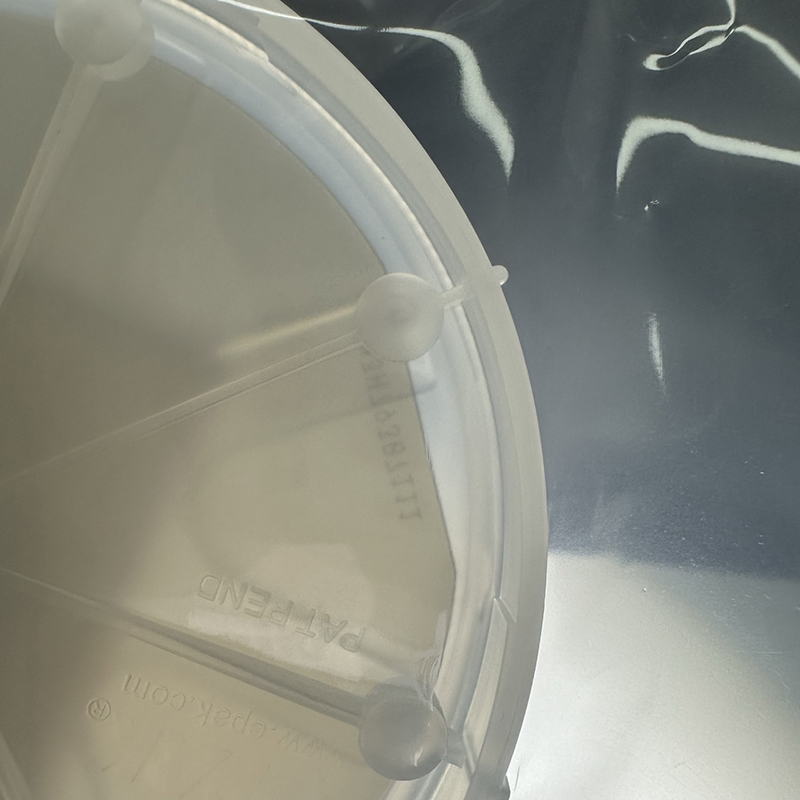

| Emballage | Multi-wafer-kassette eller enkelt wafer-beholder | ||||||||||

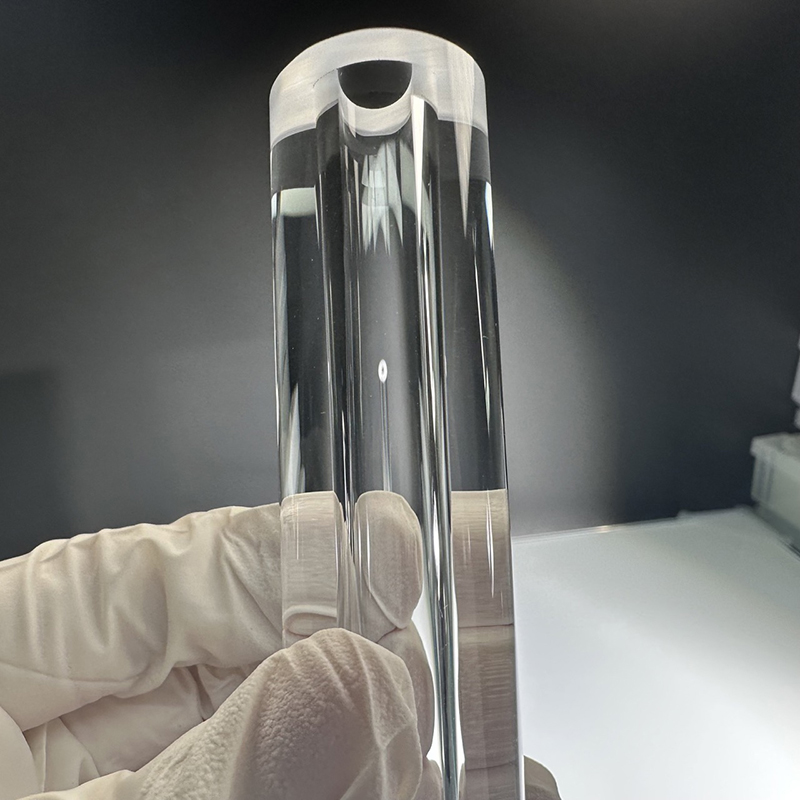

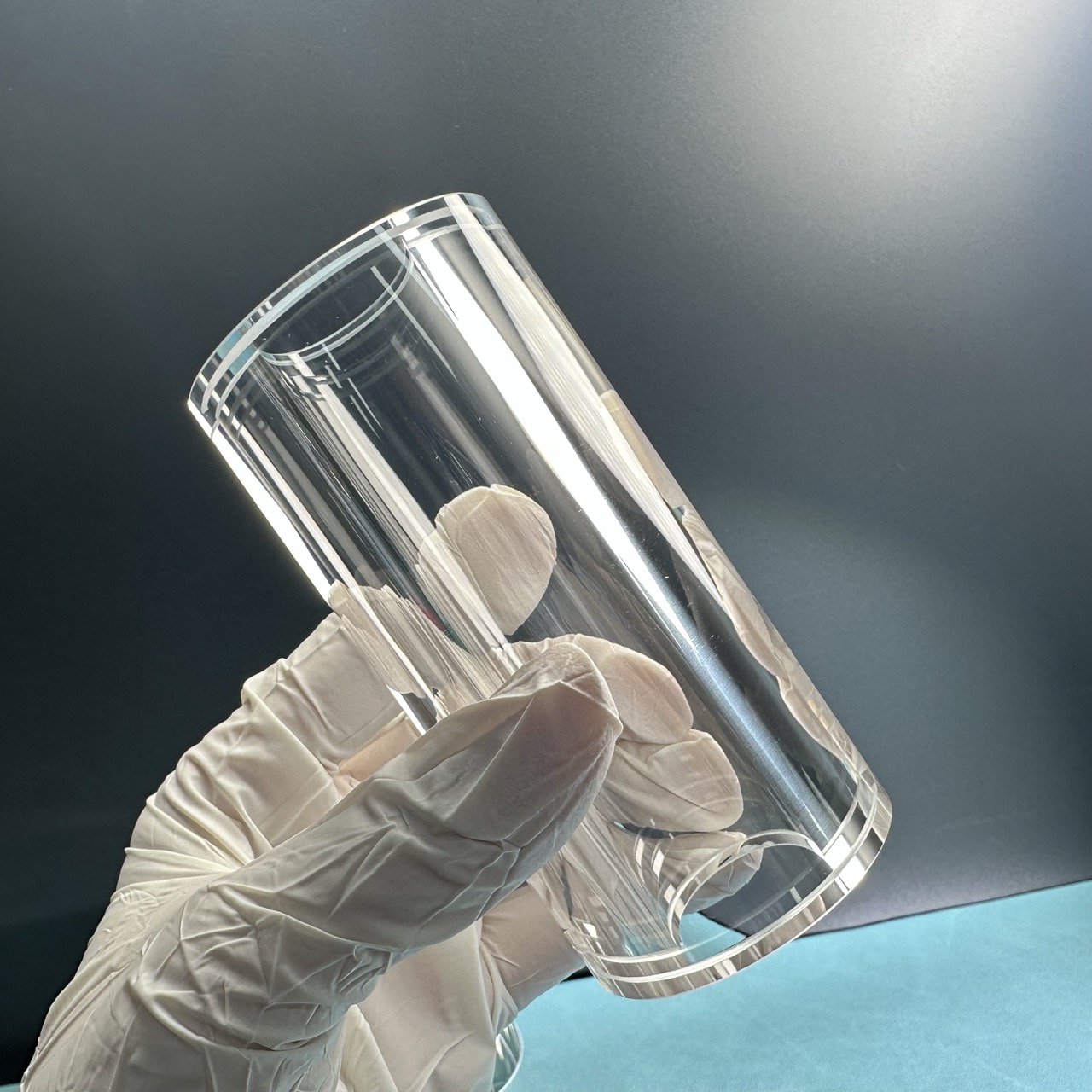

Detaljeret diagram

Skriv din besked her og send den til os